Защищенный режим (Protected Mode)

Основным режимом работы МП является защищенный режим. Ключевые особенности защищенного режима: виртуальное адресное пространство, защита и многозадачность. МП может быть переведен в защищенный режим установкой бита 0 (Protect Enable) в регистре CR0. Вернуться в режим реального адреса МП может по сигналу RESET или сбросом бита PE (в Intel-286 недоступно).

В защищенном режиме программа оперирует с адресами, которые могут относиться к физически отсутствующим ячейкам памяти, поэтому такое адресное пространство называется виртуальным. Размер виртуального адресного пространства программы может превышать емкость физической памяти и достигать 64Тбайт.

Преобразование логического адреса в физический происходит в два этапа: сначала блок управления сегментами выполняет трансляцию адреса в соответствии с сегментированной моделью памяти, получая 32-битный линейный адрес, а затем блок страничного преобразования выполняет разбиение на страницы, преобразуя 32-битный линейный адрес в 32-битный или 36-битный (P6) физический. МП не предусматривает механизмов запрещения сегментации; с другой стороны, страничная трансляция есть опциональный механизм и может использоваться либо не использоваться в зависимости от особенностей операционной системы.

В рамках сегментированной модели адресации для программы память представляется группой независимых адресных блоков, называемых сегментами. Для адресации байта памяти программа должна использовать логический адрес, состоящий из селектора сегмента и смещения. Селектор сегмента выбирает определенный сегмент, а смещение указывает на конкретный байт в адресном пространстве выбранного сегмента. Селектор сегмента может находиться либо непосредственно в коде команды, либо в одном из сегментных регистров. Смещение также может либо непосредственно находиться в коде команды, либо вычисляться на основе значений регистров общего назначения.

С каждым сегментом связана особая структура, хранящая информацию о нем: дескриптор. Дескриптор - это 8-байтная единица описательной информации, распознаваемая устройством управления памятью в защищенном режиме, хранящаяся в дескрипторной таблице.

Дескриптор сегмента содержит базовый адрес описываемого сегмента, предел сегмента и права доступа к сегменту. В защищенном режиме сегменты могут начинаться с любого линейного адреса (который называется базовым адресом сегмента) и иметь любой предел вплоть до 4Гбайт.

Дескрипторные таблицы - это массивы памяти переменной длины, содержащие 8-байтные элементы: дескрипторы. Дескрипторная таблица может иметь длину от 8 байт до 64 Кбайт и в каждой таблице может быть до 8192 дескрипторов. Существуют две обязательных дескрипторных таблицы - глобальная дескрипторная таблица (Global Descriptor Table - GDT) и дескрипторная таблица прерывания (Interrupt Descriptor Table - IDT), а также множество (вплоть до 8191) необязательных локальных дескрипторных таблиц (Local Descriptor Table - LDT), из которых в каждый момент времени процессору доступна только одна. Расположение дескрипторных таблиц определяется регистрами процессора GDTR, IDTR, LDTR.

GDT содержит дескрипторы, доступные всем задачам в системе. GDT может содержать дескрипторы любых типов: и дескрипторы сегментов, и системные дескрипторы (кроме шлюзов прерываний и ловушек). Первый элемент GDT (с нулевым индексом) не используется. Ему соответствует нуль-селектор, обозначающий "пустой" указатель.

LDT обеспечивают способ изоляции сегментов программы и данных исполняемой задачи от других задач. LDT связана с конкретной задачей и может содержать только дескрипторы сегментов, шлюзы вызовов и шлюзы задач.

Сегмент не может быть доступен задаче, если его дескриптор не существует ни в текущей таблице LDT, ни в таблице GDT. Использование двух дескрипторных таблиц позволяет, с одной стороны, изолировать и защищать сегменты исполняемой задачи, а с другой - позволяет разделять глобальные данные и код между различными задачами.

IDT может содержать только шлюзы задач, шлюзы прерываний или шлюзы ловушек.

Для вычисления линейного адреса МП выполняет следующие действия (рис. 4.1):

- МП использует селектор сегмента для нахождения дескриптора сегмента.

Селектор содержит индекс дескриптора в дескрипторной таблице (Index), бит TI, определяющий, к какой дескрипторной таблице производится обращение (LDT или GDT), а также запрашиваемые права доступа к сегменту (RPL). Если селектор хранится в сегментном регистре, то обращение к дескрипторным таблицам происходит только при загрузке селектора в сегментный регистр, т. к. каждый сегментный регистр хранит соответствующий дескриптор в программно-недоступном ("теневом") регистре-кэше. - МП анализирует дескриптор сегмента, контролируя права доступа (сегмент доступен с текущего уровня привилегий) и предел сегмента (смещение не превышает предел);

- МП добавляет смещение к базовому адресу сегмента и получает линейный адрес.

Если страничная трансляция отключена, то сформированный линейный адрес считается физическим и выставляется на шину процессора для выполнения цикла чтения или записи памяти.

Рис. 4.1. Схема преобразования логического адреса в линейный

Механизм сегментации обеспечивает превосходную защиту, но он не очень удобен для реализации виртуальной памяти (подкачки). В дескрипторе сегмента есть бит присутствия, по нему процессор определяет, находится ли данный сегмент в физической памяти или на внешнем запоминающем устройстве (на винчестере). В последнем случае генерируется исключение #11, обработчик которого может подгрузить сегмент в память. Неудобство заключается в том, что различные сегменты могут иметь различную длину. Этого можно избежать, если механизм подкачки реализовывать на основе страничного преобразования. Особенностью этого преобразования является то, что процессор в этом случае оперирует с блоками физической памяти равной длины (4 Кбайт) - страницами. Страницы не имеют непосредственного отношения к логической структуре программы. Кроме того, в МП подсемейства P6 страничная трансляция обеспечивает 36-битную физическую адресацию памяти (64 Гбайт). Страничное преобразование действует только в защищенном режиме и включается установкой в 1 бита PG в регистре CR0.

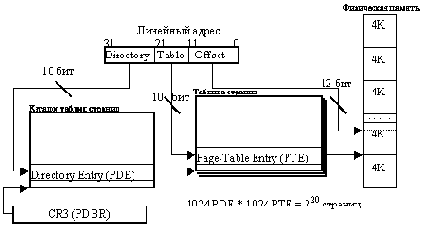

В страничном преобразовании участвуют два типа структур: каталоги таблиц (Page Directory) и таблицы страниц (Page Table). Эти структуры состоят из 1024 32-битных элементов. Элементы содержат старшие 20 бит физического адреса адресуемых объектов. Элементы таблицы страниц (Page Table Entry - PTE) адресуют страницы, а элементы каталога таблиц (Page Directory Entry - PDE) адресуют таблицы страниц. Старшие 20 бит физического адреса каталога таблиц хранятся в регистре CR3 (Page Directory Base Register - PDBR) (это единственный регистр процессора, который содержит физический адрес памяти). Все структуры выровнены по границе страницы.

Рис. 4.2. Стандартная 2-уровневая схема страничной трансляции

В процессе страничной трансляции адресов полученный линейный адрес разбивается на три части. Старшие десять бит (Directory) линейного адреса являются индексом элемента из каталога таблиц. По этому элементу определяется физический адрес таблицы страниц. Биты 21-12 (Table) линейного адреса выбирают элемент из этой таблицы страниц. Выбранный элемент определяет физический адрес страницы. Младшие 12 бит (Offset) линейного адреса определяют смещение от начала страницы.

Страницы начинаются на границах 4 Кбайт областей памяти, поэтому младшие 12 бит адреса страницы всегда равны нулю. В каталоге таблиц элементы хранят физические адреса таблиц страниц. В таблице страниц элементы хранят физические адреса самих страниц.

В МП Pentium фирма Intel реализовала новую возможность - расширение размера страниц (Page Size Extension - PSE). PSE позволяет использовать страницы размером 4 Мбайт и одноуровневый механизм страничной трансляции.

В подсемействе P6 шина адреса была расширена до 36 бит. Соответственно, процессоры Pentium Pro, Pentium II, Pentium III и более поздние способны адресовать до 64 Гбайт физической памяти. Эта возможность называется расширением физического адреса (Physical Address Extension - PAE) и доступна только при использовании страничной трансляции.

Использование PSE и PAE следующим образом влияет на страничное преобразование:

| 0 | X | x | x | - | 32 бит |

| 1 | 0 | 0 | x | 4 Кб | 32 бит |

| 1 | 0 | 1 | 0 | 4 Кб | 32 бит |

| 1 | 0 | 1 | 1 | 4 Мб | 32 бит |

| 1 | 1 | x | 0 | 4 Кб | 32 бит |

| 1 | 1 | x | 1 | 2 Мб | 32 бит |

Среда задачи состоит из содержимого регистров МП и всего кода с данными в пространстве памяти. МП способен быстро переключаться из одной среды выполнения в другую, имитируя параллельную работу нескольких задач. Для некоторых задач может эмулироваться управление памятью, как у МП 8086. Такое состояние задачи называется режимом виртуального 8086 (Virtual 8086 Mode). О пребывании задачи в данном состоянии сигнализирует бит VM в регистре флагов. При этом задачи виртуального МП 8086 изолированы и защищены, как от друг друга, так и от обычных задач защищенного режима.

Задачу составляют два компонента: адресное пространство задачи и сегмент состояния задачи (Task State Segment - TSS).

В адресное пространство задачи входят доступные ей сегменты кода, данных и стека. Если используется механизм привилегий, то каждой задаче должны быть предоставлены сегменты стека для всех используемых уровней привилегий.

Сегмент состояния задачи хранит состояние регистров (контекст) процессора:

- состояние сегментных регистров (селекторы сегментов, формирующие адресное пространство задачи);

- состояние регистров общего назначения;

- состояние регистра флагов (EFLAGS);

- указатель очередной команды (EIP);

- значение регистра CR3 (PDBR);

- значение регистра LDTR.

В многозадачных системах TSS предоставляет механизм для связывания (вложения) задач.

Каждая задача идентифицируется селектором соответствующего ей TSS. Этот селектор загружается в регистр задачи (Task Register - TR) при переключении на задачу. В теневую часть регистра загружаются базовый адрес, предел и атрибуты TSS. Операционная система может предусматривать для каждой задачи свое линейное адресное пространство (свой набор страниц для страничного преобразования), тогда при переключении задачи загружается и регистр CR3 (PDBR), хранящий адрес каталога таблиц для страничного преобразования.

В защищенном режиме процессор обеспечивает определенные механизмы защиты на основе сегментации и на основе страничного преобразования. Механизмы защиты позволяют ограничивать доступ к определенным сегментам или страницам при помощи уровней привилегий (4 для сегментов и 2 для страниц). Например, критические код и данные операционной системы могут быть расположены на более привилегированном уровне, чем прикладные программы. Это позволит ограничить и контролировать доступ прикладных программ к функциям и данным операционной системы.

Механизм защиты обеспечивает соответствие любой ссылки на ячейки памяти определенным условиям. Все проверки выполняются до начала цикла обращения к памяти. Нарушение любого условия приводит к генерации исключения. Проверки выполняются параллельно с формированием адреса и поэтому не ухудшают производительность процессора. Все ссылки должны пройти следующие проверки:

- контроль предела;

- контроль типа;

- контроль уровня привилегий;

- контроль выравнивания;

- ограничение адресного пространства;

- ограничение точек входа в процедуры (для шлюзов);

- ограничение набора команд (привилегированные инструкции).

В защищенном режиме нет способа отключить механизм защиты. Даже если назначить всем сегментам и задачам нулевой (самый высший) уровень привилегий, все равно будут выполняться проверки контроля предела и типа. В то же время, механизм защиты на уровне страниц можно подавить, если назначить всем страницам уровень привилегий суперпользователя и обеспечить доступ на чтение и запись.

Контроль пределов и типов сегментов обеспечивает целостность сегментов кода и данных. Программа не имеет права обратиться к виртуальной памяти, выходящей за предел того или иного сегмента. Программа не имеет права обратиться к сегменту данных как к коду, и наоборот.

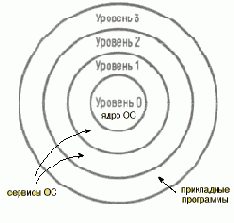

Архитектура защиты МП обеспечивает 4 иерархических уровня привилегий, что позволяет ограничить задаче доступ к отдельным сегментам в зависимости от ее текущих привилегий. Привилегии - это свойство (обычно устанавливаемое при проектировании системы), которое определяет, какие компьютерные операции разрешаются в любой момент времени и какие доступы к памяти законны. Привилегии используются для обеспечения безопасности в компьютерной системе. Привилегии реализуются путем присвоения значения от 0 до 3 ключевым объектам, которые опознаются процессором. Значение 0 соответствует наибольшим привилегиям, тогда как значение 3 - наименьшим.

Четыре уровня привилегий можно интерпретировать в виде колец защиты (рис. 4.3). Центр (уровень 0) предназначен для сегментов, содержащих наиболее критичные программы (обычно ядро операционной системы). Внешние кольца предназначены для сегментов с менее критичными программами или данными. Использование всех четырех уровней привилегий не является необходимым. Существующие системы, спроектированные с меньшим количеством уровней, могут просто игнорировать другие допустимые уровни. UNIX и Windows, например, используют только два уровня привилегий: 0 (для ядра системы) и 3 (для всего остального), а OS/2 использует уровни 0 (для ядра системы), 2 (для процедур ввода-вывода) и 3 (для прикладных программ).

Рис. 4.3. Интерпретация уровней привилегий в виде колец защиты

Механизм контроля уровня привилегий микропроцессора оперирует следующими значениями:

CPL - текущий уровень привилегий (Current Privilege Level): уровень привилегий, на котором в данный момент исполняется задача. Значение CPL хранится в поле RPL селектора сегмента кода, который помещен в регистр CS. Обычно это значение соответствует уровню привилегий дескриптора исполняемого сегмента кода. Уровень привилегий меняется, когда управление передается сегменту кода с другим значением DPL (за исключением подчиняемых сегментов кода).

DPL - уровень привилегий дескриптора (Descriptor Privilege Level): наименее привилегированный уровень, на котором задача может получить доступ к сегменту или шлюзу, связанному с этим дескриптором. Уровень DPL определяется битами 46 и 45 дескриптора.

RPL - запрашиваемый уровень привилегий (Requested Privilege Level) используется для временного понижения своего уровня привилегий при обращении к памяти. RPL заносится в младшие биты селектора.

Механизм контроля уровня привилегий обычно сравнивает уровень привилегий дескриптора (DPL) с максимальным из двух чисел CPL и RPL. Наименее привилегированный из текущего уровня привилегий и запрашиваемого считается эффективным уровнем привилегий: EPL = max (CPL, RPL).

Контроль привилегий при доступе к данным осуществляется при загрузке селектора в сегментный регистр DS, ES, FS, GS (либо при обращении к памяти, если селектор содержится в коде инструкции). Программа может обратиться к сегменту данных, который находится на том же или более низком уровне привилегий (с учетом RPL), т.е. доступ к данным разрешен, если max(CPL, RPL)<= DPL; в противном случае генерируется нарушение общей защиты.

Контроль привилегий при доступе к стеку осуществляется при загрузке селектора в регистр SS. Программа должна использовать сегмент стека, находящийся на том же уровне привилегий, т.е. CPL = RPL = DPL.

Для передачи управления на обычный сегмент кода его уровень привилегий должен совпадать с текущим уровнем привилегий.

Значение RPL должно быть не больше CPL, чтобы не вызывать исключения, но вне зависимости от значения RPL уровень привилегий не изменится: CPL = DPL. Текущий уровень привилегий может измениться при передаче управления через селектор шлюза. Шлюзы бывают четырех типов: шлюз вызова, шлюз задачи, шлюз ловушки и шлюз прерывания (последние два типа не используются в командах перехода и вызова). При передаче управления через селектор шлюза задачи или селектор TSS происходит переключение задач. Одна задача может передать управление другой задаче, при этом контролируется, чтобы объект, через который передается управление, был на том же или более низком уровне привилегий, чем CPL (правило контроля как для сегментов данных).

Кроме того, текущий уровень привилегий задачи влияет на возможность выполнения тех или иных специфических команд (привилегированных инструкций). Кроме привилегированных, существуют инструкции, результат выполнения которых зависит от поля IOPL в регистре флагов (I/O Privilege Level - уровень привилегий ввода-вывода): IN, INS, OUT, OUTS, CLI, STI. Механизм защиты процессора позволяет выполнять эти инструкции, только если задача обладает достаточными привилегиями, т.е. CPL <= IOPL.

Функции страничной трансляции, впервые появившиеся в Intel386, обеспечивают дополнительные механизмы защиты на уровне страниц. Особенно это удобно при использовании сплошной модели памяти, когда и операционная система, и прикладные программы работают в едином пространстве логических адресов, т.к. защита на уровне страниц может обеспечить разграничение привилегий для страниц операционной системы и прикладных программ. Защита на уровне страниц предоставляет два типа контроля: ограничение адресного пространства (страницы супервизора и страницы пользователя) и ограничение типа доступа (доступ только для чтения и доступ на чтение-запись). Если проверки не проходят, генерируется страничное нарушение (исключение #14).

Ограничение адресного пространства на уровне страниц обеспечивается двумя уровнями привилегий: режим супервизора (уровень 0) и режим пользователя (уровень 1).

Режим супервизора соответствует привилегиям на уровне сегментов CPL = 0, CPL = 1 и CPL = 2. В режиме супервизора доступны все страницы. Режим пользователя соответствует привилегиям на уровне сегментов CPL = 3. В режиме пользователя доступны только страницы пользователя. В адресное пространство супервизора попадают страницы, для которых соответствующий элемент таблицы страниц или каталога таблиц содержит бит US = 0. В адресное пространство пользователя попадают страницы, для которых и соответствующий элемент таблицы страниц, и соответствующий элемент каталога таблиц содержат бит US = 1.

В МП Intel-386 ограничение типа доступа применяется только в адресном пространстве пользователя. Программа в режиме пользователя имеет право изменять только те страницы, для которых и соответствующий элемент таблицы страниц, и соответствующий элемент каталога таблиц содержат бит RW = 1. Если для какой-либо страницы элемент таблицы страниц или элемент каталога таблиц содержит бит RW = 0, то страница доступна только для чтения. В режиме супервизора все страницы доступны и для чтения, и для записи.

Когда используются оба вида защиты и на уровне страниц, и на уровне сегментов, процессор сначала выполняет проверки защиты сегментов, и только в случае успеха - проверки защиты страниц. Т.е. если доступ к памяти отвергается защитой на уровне сегментов, то будет сгенерировано нарушение общей защиты, а проверки защиты страниц выполняться не будут и дополнительно страничное нарушение не возникнет. Если проверки защиты сегментов проходят успешно, но нарушаются правила защиты страниц, генерируется страничное нарушение. Доступ к памяти предоставляется, только когда выполнены все правила и для сегментов, и для страниц.

В табл. 4.2 представлены сводные характеристики режимов IA-32.

| Формирование линейного адреса | без дескрипторных таблиц | через дескрипторную таблицу | без дескрипторных таблиц | без дескрипторных таблиц |

| Предел сегментов | 64 Кб | определяется дескриптором | 64 Кб | 4 Гб |

| Размер адреса/данных по умолчанию | 16 бит | определяется дескриптором | 16 бит | 16 бит |

| Максимальный объем доступной памяти (виртуальной) | ~1 Мб | ~64 Тб | ~1 Мб | ~4 Гб |

| Защита | нет1) | да | да | нет |

| Страничная трансляция | нет | да | да | нет |

| Многозадачность | нет | да | да | нет |

| Обработка прерываний | таблица векторов | дескрипторная таблица | дескрипторная таблица | нет2) |